### **Konrad Möller**

# Run-time Reconfigurable Constant Multiplication on Field Programmable Gate Arrays

Konrad Möller

Run-time Reconfigurable Constant Multiplication on Field Programmable Gate Arrays

This work has been accepted by the Faculty of Electrical Engineering / Computer Science of the University of Kassel as a thesis for acquiring the academic degree of Doktor der Ingenieurwissenschaften (Dr.-Ing.).

Supervisor: Prof. Dr.-Ing. Peter Zipf, University of Kassel

Co-Supervisor: Prof. Dr.-Ing. Uwe Meyer-Baese, Florida A&M University – Florida State University

College of Engineering

Defense day: 11<sup>th</sup> August 2017

Bibliographic information published by Deutsche Nationalbibliothek

The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie;

detailed bibliographic data is available in the Internet at <a href="http://dnb.dnb.de">http://dnb.dnb.de</a>.

Zugl.: Kassel, Univ., Diss. 2017 ISBN 978-3-7376-0376-8 (print) ISBN 978-3-7376-0377-5 (e-book)

DOI: http://dx.medra.org/10.19211/KUP9783737603775 URN: http://nbn-resolving.de/urn:nbn:de:0002-403772

© 2017, kassel university press GmbH, Kassel www.upress.uni-kassel.de

Printed in Germany

## **Abstract**

This thesis addresses the question how run-time reconfigurable constant multipliers (RCMs) can be efficiently implemented on field programmable gate arrays (FPGAs). RCMs calculate the multiplication of an input number by one out of several constants which can be selected dynamically during run-time. The evaluation of RCMs is done by considering three different reconfiguration principles, namely: reconfiguration using reconfigurable look-up tables (LUTs), reconfiguration using multiplexers and Partial Reconfiguration (PR). While solutions for the latter one are already provided by the FPGA vendor's software tools, this thesis contributes two new methods to generate RCMs using the first two reconfiguration principles. First, a LUT-based constant multiplier is extended to be reconfigurable. Second, optimized constant multipliers without reconfiguration are fused using multiplexers. Moreover, a general post-optimization for multiplexer-based RCMs is proposed. Finally, the design space produced in this way is analyzed using synthesis experiments. The contributed methods provide some important trade-off points in the design space of run-time reconfigurable constant multiplication on FPGAs. This is important as constant multiplication is an essential operation in digital signal processing (DSP) applications. Furthermore, FPGAs become more and more important for DSP applications which were traditionally implemented using application specific integrated circuits (ASICs). As FPGAs have an inherent inefficiency caused by their re-programmability, trade-offs and target optimized FPGA implementations are required to narrow the gap to equivalent ASIC implementations.

## Acknowledgements

First of all, I want to thank my wife Sarah and my parents Elfriede and Winfried for their unconditioned support in all life challenges.

I especially want to thank Peter Zipf for supervising this thesis and for supporting my work in the Digital Technology Group of the University of Kassel in all its facets. I am especially thankful for his excellent guidance and his confidence in my skills. Next, I want to kindly thank my colleague Martin Kumm for always being interested in my work and many fruitful common projects. Martin and Peter were always available to discuss research questions. These discussions brought forth new ideas and helped to focus on the right aspects of a topic.

A big thanks to all the students that supported parts of this thesis during their project work, student job and master's thesis. In particular, I would like to emphasize the work of Marco Kleinlein on the VHDL code generator and the PAG fusion implementation and the work of Björn Barschtipan on reconfigurable multiplier block extensions.

Next, I want to thank Mario Garrido from the University of Linköping, Sweden, and Uwe Meyer-Baese from the Florida State University, USA for their confirmation of my work during their stay at the University of Kassel. Special thanks to Mario for our collaboration on multiplexer-based reconfigurable constant multiplication and to Uwe for reviewing this thesis as second assessor.

I also want to thank the mathematicians Diana Fanghänel, Evelyn Lerche and Dörthe Janssen for being interested in my research and for their help with mathematical questions.

I appreciate the financial support and the recognition of the research questions of this thesis by the GSI Helmholtzzentrum für Schwerionenforschung Darmstadt (GSI) and the Deutsche Forschungsgemeinschaft (DFG).

Finally, I want to thank the whole current and former team of the Digital Technology Group for administrative help, a good cooperation and fruitful discussions.

## Contents

| Αl | bstra | ct      |                                                                            | ii  |

|----|-------|---------|----------------------------------------------------------------------------|-----|

| A  | cknov | vledgei | ments                                                                      | \   |

| Li | st of | Figure  | s                                                                          | ×   |

| Li | st of | Tables  | ;                                                                          | X۱  |

| Αl | bbrev | iations |                                                                            | xvi |

| Αı | uthor | 's Pub  | lications                                                                  | xix |

| 1  | Intr  | oductio | on                                                                         | 1   |

|    | 1.1   | Motiv   | ation                                                                      |     |

|    | 1.2   |         | nization and Contributions of the Thesis                                   |     |

| 2  | Bac   | kgrour  | nd                                                                         | 5   |

|    | 2.1   | Field   | Programmable Gate Arrays                                                   | 5   |

|    |       | 2.1.1   | Architectural Features                                                     | 6   |

|    |       | 2.1.2   | Design Flow                                                                | 10  |

|    | 2.2   | Run-T   | Fime Reconfiguration on Field Programmable Gate Arrays $\ \ldots \ \ldots$ | 12  |

|    |       | 2.2.1   | Partial Reconfiguration                                                    | 12  |

|    |       | 2.2.2   | Logic Reconfiguration using Dynamically Reconfigurable LUTs .              | 13  |

|    |       | 2.2.3   | Routing Reconfiguration using Logic Multiplexers on FPGAs                  | 15  |

|    |       | 2.2.4   | Evaluation of Run-Time Reconfigurable Designs                              | 16  |

|    | 2.3   | Const   | ant Multiplication on Integrated Circuits                                  | 19  |

|    |       | 2.3.1   | Single Constant Multiplication                                             | 19  |

|    |       | 2.3.2   | Multiple Constant Multiplication                                           | 22  |

|    | 2.4   | Imple   | mentation of Constant Multiplication on FPGAs                              | 23  |

|    |       | 2.4.1   | Reduced Pipelined Adder Graph Algorithm                                    | 23  |

|    |       | 2.4.2   | Look-Up Table Based Constant Multiplication                                | 25  |

| 3  | Rec   |         | rable Constant Multiplication using LUTs                                   | 29  |

|    | 3.1   | Relate  | ed Work                                                                    | 29  |

|   | 3.2  | Dynar   | nically Reconfigurable Multiplication using LUTs            | 30  |

|---|------|---------|-------------------------------------------------------------|-----|

|   |      | 3.2.1   | Architectural Preliminaries                                 | 30  |

|   |      | 3.2.2   | LUT Reconfiguration                                         | 31  |

|   |      | 3.2.3   | Implementation                                              | 34  |

|   |      | 3.2.4   | Experimental Evaluation                                     | 34  |

|   |      | 3.2.5   | Relevance of the Results                                    | 37  |

|   | 3.3  | Applie  | eation of LUT Reconfiguration in Reconfigurable FIR Filters | 38  |

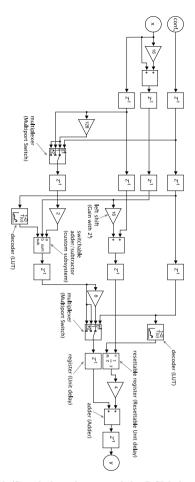

|   |      | 3.3.1   | Direct Approach                                             | 38  |

|   |      | 3.3.2   | Distributed Arithmetic Approach                             | 38  |

|   |      | 3.3.3   | Comparison of Both Approaches                               | 42  |

|   | 3.4  | Conclu  | ısion                                                       | 46  |

| 4 | Mul  | •       | r-based Reconfigurable Constant Multiplication              | 47  |

|   | 4.1  | Relate  | d Work                                                      | 48  |

|   |      | 4.1.1   | Basic Computation Kernel Algorithms                         | 49  |

|   |      | 4.1.2   | Fusion of Constant Multipliers                              | 50  |

|   | 4.2  | Recon   | figurable Constant Multiplication for FPGAs                 | 52  |

|   |      | 4.2.1   | Pipelined Adder Graph Fusion                                | 52  |

|   |      | 4.2.2   | Advanced Features of the Algorithm                          | 59  |

|   |      | 4.2.3   | Implementation                                              | 64  |

|   |      | 4.2.4   | Experimental Evaluation                                     | 65  |

|   | 4.3  | Concli  | ısion                                                       | 71  |

| 5 |      |         | g Shifts in Multiplexer-based Reconfigurable Constant Multi |     |

|   | plie |         |                                                             | 73  |

|   | 5.1  | _       | round and Related Work                                      | 73  |

|   | 5.2  | _       | al Shift Reassignment in Multiplexer-based RCMs             | 74  |

|   |      | 5.2.1   | Optimal Shift Reassignment Method                           | 75  |

|   |      | 5.2.2   | Experimental Evaluation                                     | 78  |

|   | 5.3  | Concli  | ısion                                                       | 81  |

| 6 | Des  | ign Spa | ace of Run-Time Reconfiguration Methods                     | 83  |

|   | 6.1  | Design  | Space of a Reconfigurable FIR Filter                        | 83  |

|   |      | 6.1.1   | Experimental Setup                                          | 84  |

|   |      | 6.1.2   | Experimental Results                                        | 85  |

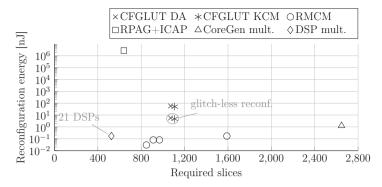

|   |      | 6.1.3   | Energy per Sample and Reconfiguration Energy                | 88  |

|   | 6.2  | Conclu  | ısion                                                       | 90  |

| 7 | Con  | clusion |                                                             | 93  |

| В | Futi | ure Wo  | rk                                                          | 95  |

|   | Q 1  | Errton  | rion of the DDAC Algorithm                                  | 0.0 |

|    | 8.2   | Reuse of Linear Subcircuits in Time-Multiplex                                 | 96  |

|----|-------|-------------------------------------------------------------------------------|-----|

| Α  | Det   | ailed Complexity Consideration of Optimal PAG Fusion                          | 97  |

|    | A.1   | Determining the Number of Solutions and Decisions                             | 97  |

|    | A.2   | Upper Bound for the Number of Decisions $\ \ldots \ \ldots \ \ldots \ \ldots$ | 98  |

| В  | Dat   | a of the Experimental Evaluation                                              | 99  |

| С  | Syn   | tax for Reconfigurable Pipelined Adder Graphs                                 | 103 |

| D  | Rec   | onfigurable Constant Multiplier Integration in Origami HLS                    | 105 |

| Ε  | FIR   | Benchmark for the Design Space Exploration                                    | 107 |

| Bi | hliog | ranhv                                                                         | 100 |

# List of Figures

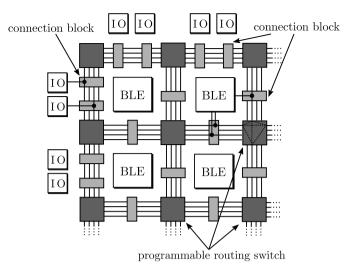

| 2.1  | Simplified overview of an FPGA layout                                                                           | 6  |

|------|-----------------------------------------------------------------------------------------------------------------|----|

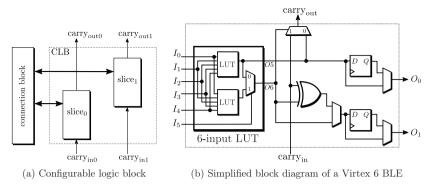

| 2.2  | Xilinx Virtex 6 BLE and its clustering to a slice and a CLB                                                     | 7  |

| 2.3  | Intel Stratix V ALM and its clustering to an LAB                                                                | 8  |

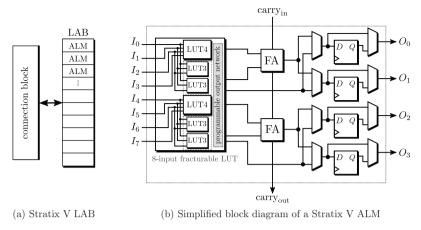

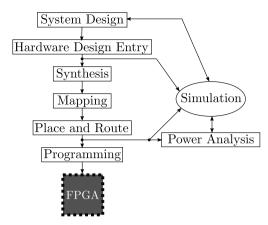

| 2.4  | Diagram of the steps required to map a system specification to an FPGA.                                         | 11 |

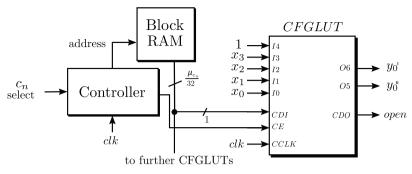

| 2.5  | Specialized Xilinx FPGA components to enable LUT reconfiguration:                                               |    |

|      | (a) interface of a Xilinx CFGLUT, (b) reduced block diagram to show                                             |    |

|      | the functionality of a Xilinx shift register LUT. $\hdots$                                                      | 14 |

| 2.6  | Mapping of a 1 bit 16:1 multiplexer into a Virtex 6 slice                                                       | 16 |

| 2.7  | Required LUTs per bit for an x:1 multiplexer on a Virtex 6 FPGA. ISE                                            |    |

|      | solution (gray) and improvement by $Primitive$ usage, using the multi-                                          |    |

|      | plexer implementation described by Chapman                                                                      | 17 |

| 2.8  | Required ALUTs per bit for an x:1 multiplexer on a Stratix V FPGA                                               |    |

|      | using Quartus.                                                                                                  | 17 |

| 2.9  | $\label{lem:multiplication} \mbox{Multiplier-less constant multiplication with different realization methods}.$ | 20 |

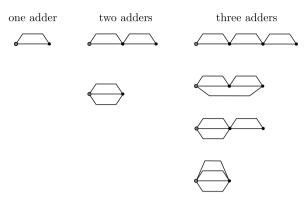

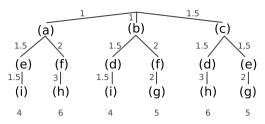

| 2.10 | Adder topologies for up to three adders from Gustafsson et al. [5]                                              | 21 |

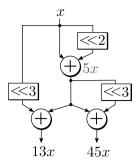

| 2.11 | Example of an MCM circuit for the multiplication $45x$ and $13x$ with                                           |    |

|      | reused intermediate result                                                                                      | 22 |

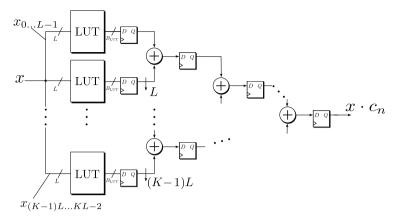

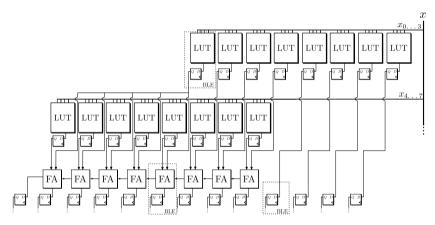

| 2.12 | LUT-based constant multiplication using a pipelined adder tree                                                  | 27 |

| 2.13 | Example implementation of an $8\times 4$ bit LUT-based signed multiplier                                        | 27 |

| 3.1  | Architecture for the configuration update using pre-calculated configu-                                         |    |

|      | rations                                                                                                         | 32 |

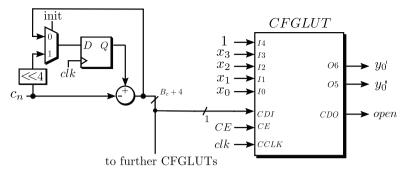

| 3.2  |                                                                                                                 | 33 |

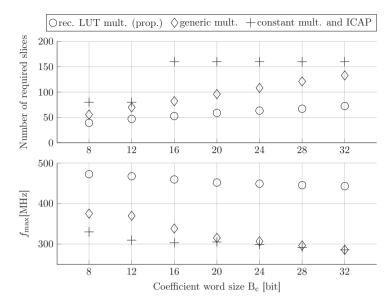

| 3.3  | Comparison of slice utilization and frequency of the proposed reconfig-                                         |    |

|      | urable KCM-based design with a generic multiplier and a reconfigurable                                          |    |

|      | constant multiplier using ICAP. The shown values are average values for                                         |    |

|      | variations of the input word size $B_x$ over the coefficient word size $B_c$                                    | 35 |

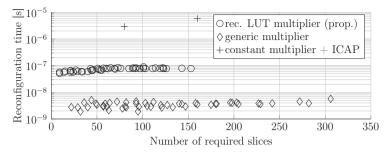

| 3.4  | Reconfiguration time in seconds over required slices for the different                                          |    |

|      | reconfigurable multiplier implementations.                                                                      | 38 |

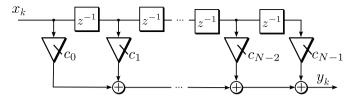

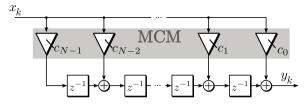

| 3.5  | Block diagram of an FIR filter in direct form.                                                                  | 39 |

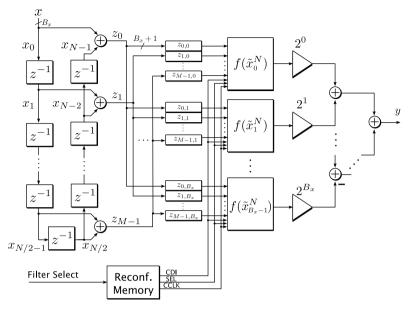

| 3.6  | Block diagram of an N-tap even symmetric reconfigurable DA FIR filter.                                          | 41 |

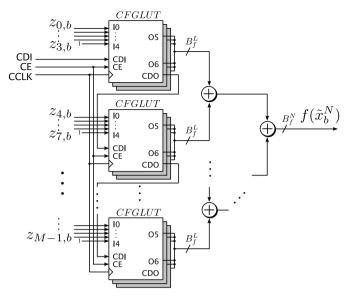

| 3.7  | Realization of the reconfigurable function $f(\tilde{x}_b^N)$ using CFGLUTs                                     | 42 |

| 4.1  | Example of an RCM computing $12305x$ or $20746x$                                                                | 47 |

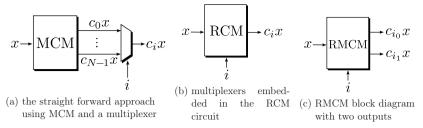

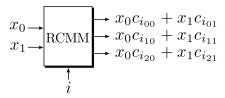

| 4.2         | Block diagrams for reconfigurable constant multiplication variants                                                                                                                                                             | 48 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

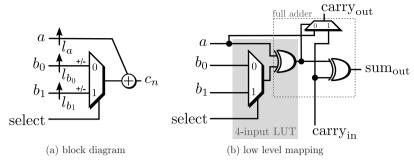

| 4.3         | Basic computation kernel for a 4-input LUT FPGA                                                                                                                                                                                | 50 |

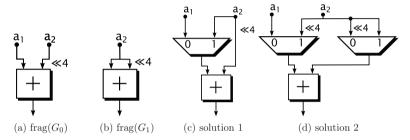

| 4.4         | Example fusion of two fragments $frag(G_0)$ and $frag(G_1)$                                                                                                                                                                    | 50 |

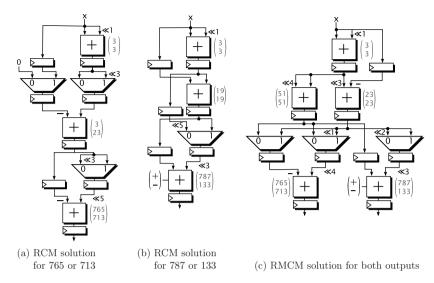

| 4.5         | Realization of multiple constant sets with two RCMs or one RMCM. $$ .                                                                                                                                                          | 53 |

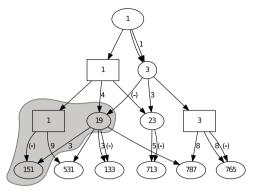

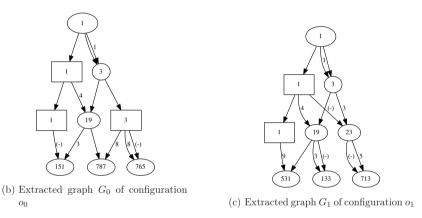

| 4.6         | Adder graphs to illustrate the optimization entry point of the PAG fusion.                                                                                                                                                     | 54 |

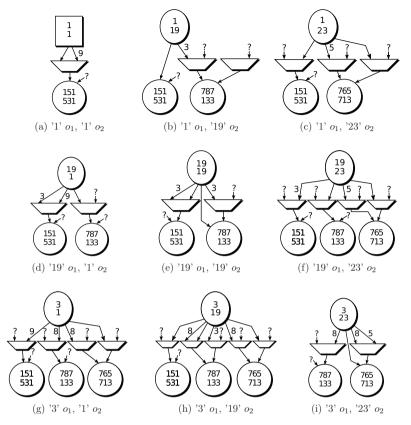

| 4.7         | All combinations of nodes in stage 2 for the configurations $o_1$ and $o_2$ .                                                                                                                                                  | 55 |

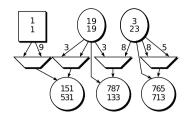

| 4.8         | Example of a valid selection for stage 2 in the running example                                                                                                                                                                | 56 |

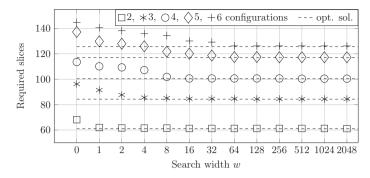

| 4.9<br>4.10 | Decision tree for the fusion of stage 2 with the combinations of Figure 4.7 Listing of the main recursion of the fusion algorithm. Inputs are the output mapping $O$ of stage $s+1$ , current stage $s$ , the search width $w$ | 57 |

|             | and the costs of the current branch $\mathit{cur\_costs}.$                                                                                                                                                                     | 58 |

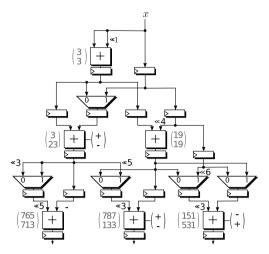

| 4.11        | RMCM solution for $o_0 = (765, 787, 151)$ and $o_1 = (713, 133, 531)$                                                                                                                                                          | 59 |

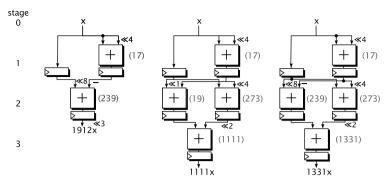

| 4.12        | RPAG solutions for the constants 1912, 1111, 1331                                                                                                                                                                              | 60 |

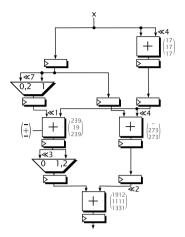

| 4.13        | Reconfigurable SCM implementation with $O = ((1912), (1111), (1331))^T$ .                                                                                                                                                      | 61 |

| 4.14        | Block diagram for a reconfigurable CMM with two inputs and three                                                                                                                                                               |    |

|             | outputs                                                                                                                                                                                                                        | 62 |

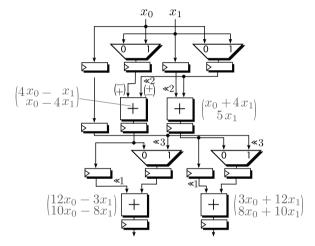

| 4.15        | Two example CMM adder graphs $\mathcal{G}_0$ and $\mathcal{G}_1$ generated with RPAG                                                                                                                                           | 63 |

| 4.16        | Reconfigurable CMM adder graph of $o_0 = (3x_0 + 12x_1, 12x_0 - 3x_1)$ and                                                                                                                                                     |    |

|             | $o_1 = (10x_0 - 8x_1, 8x_0 + 10x_1).$                                                                                                                                                                                          | 63 |

| 4.17        | Realization of switchable adder/subtractor on Xilinx Virtex 5-7 slices                                                                                                                                                         | 64 |

| 4.18        | Comparison of the average number of required slices of the heuristic with                                                                                                                                                      |    |

|             | different search widths $w$ and optimal solution (dashed lines)                                                                                                                                                                | 66 |

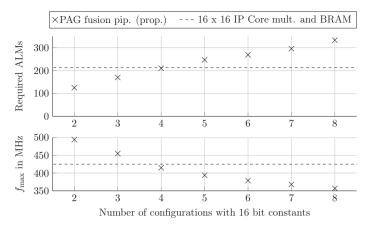

| 4.19        | Comparison of the required slices (top), the maximum clock frequency                                                                                                                                                           |    |

|             | (middle), and the slice delay product (bottom) for the proposed method, $$                                                                                                                                                     |    |

| 4.20        | DAG fusion and a generic multiplier                                                                                                                                                                                            | 68 |

|             | plementation                                                                                                                                                                                                                   | 69 |

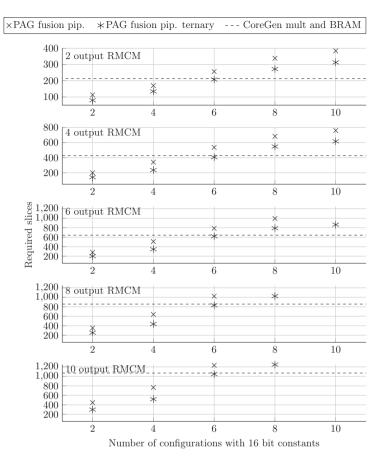

| 4.21        | Comparison of RMCM using 2-input and ternary adders to a CoreGen                                                                                                                                                               |    |

|             | soft-core multiplier implementation                                                                                                                                                                                            | 70 |

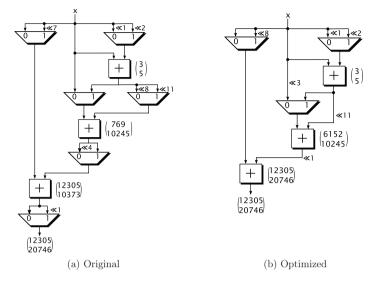

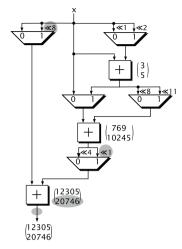

| F 1         | E 1 fd d d d DCM1 1 11 f 1 d 1                                                                                                                                                                                                 |    |

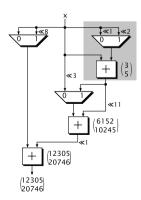

| 5.1         | Example of the optimization of an RCM based on odd fundamental                                                                                                                                                                 | 75 |

| F 9         | graphs by DAG fusion (a) with the proposed OSR approach (b)                                                                                                                                                                    | 75 |

| 5.2         | Intermediate result after step I of the optimization of the reconfigurable                                                                                                                                                     | 70 |

| F 9         | multiplier shown in Figure 5.1 (a)                                                                                                                                                                                             | 76 |

| 5.3         | Two different adder graph representations of the constant $c_0=12305$                                                                                                                                                          | 77 |

| 6.1         | Block diagram of an FIR filter in transposed form                                                                                                                                                                              | 84 |

| 6.2         | Slice delay product of the reconfigurable FIR filters compared in Ta-                                                                                                                                                          |    |

|             | ble 6.1 in slices multiplied by nano seconds.                                                                                                                                                                                  | 86 |

| 6.3 | Energy per sample over slices for the different run-time reconfigurable |     |

|-----|-------------------------------------------------------------------------|-----|

|     | FIR filter implementations                                              | 88  |

| 6.4 | Reconfiguration energy over slices for the different run-time reconfig- |     |

|     | urable FIR filter implementations                                       | 89  |

| C.1 | Example of a reconfigurable PAG G computing $21x$ or $6x$               | 104 |

| D.1 | Matlab/Simulink realization of the RCM shown in Figure 4.13             | 106 |

# List of Tables

| 2.1        | Frame size for the different Xilinx FPGA families                                                                                                                                                                             | 13       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1<br>3.2 | LUT contents for pre-calculation of constant $c_n$ ( $L=4$ ) Reconfiguration memory $\mu_x$ (for one configuration) and reconfiguration                                                                                       | 31       |

| 3.3        | times $t_{\rm rec}$ for the evaluated designs                                                                                                                                                                                 | 37       |

|            | configuration memory in bit)                                                                                                                                                                                                  | 45       |

| 4.1<br>4.2 | Cost matrix for all possible combinations in stage 2 Comparison of the average run-time of the heuristic $(w=64)$ to the                                                                                                      | 56       |

|            | optimal method and average area overhead of the heuristic solution                                                                                                                                                            | 66       |

| 5.1        | Average number of 2:1 multiplexers (MUX) for DAG fusion before and after the proposed optimal shift reassignment. Each value is the average of 100 test cases.                                                                | 79       |

| 5.2        | Average number of 2:1 multiplexers (MUX) for PAG fusion before and after the proposed multiplexer moving. Each value is the average of 100                                                                                    | 10       |

| 5.3        | test cases                                                                                                                                                                                                                    | 80       |

| 5.4        | optimal shift reassignment                                                                                                                                                                                                    | 81<br>81 |

| 6.1        | Comparison of different reconfigurable FIR filter implementations with $B_x=B_c=16\mathrm{bit}$ using CFGLUT methods, the proposed PAG fusion heuristic, ICAP reconfiguration, CoreGen multipliers and DSP block multipliers. | 86       |

| B.1        | Synthesis results in required slices and maximum clock frequency $f_{\rm max}$ in MHz for the method proposed in Section 4.2 and DAG fusion. These results are shown in Figure 4.19. Device: Virtex 6 FPGA (xc6vlx75t-        |          |

|            | 2ff484-2). Tool: Xilinx ISE v13.4                                                                                                                                                                                             | 99       |

| B.2 | Synthesis results in required ALMs and maximum clock frequency $f_{\text{max}}$ |      |

|-----|---------------------------------------------------------------------------------|------|

|     | in MHz for the method proposed in Section 4.2. These results are shown          |      |

|     | in Figure 4.20. Device: Intel Stratix V (5SGSMD3E3H29C4). Tool:                 |      |

|     | Quartus Prime 15.1                                                              | 99   |

| В.3 | Synthesis results in required slices and the maximum clock frequency            |      |

|     | $(f_{\rm max}$ in MHz) for the RMCM method proposed in Section 4.2. These       |      |

|     | results are shown in Figure 4.21 and compared to a generic CoreGen              |      |

|     | multiplier. Device: Virtex 6 FPGA (xc6vlx75t-2ff484-2). Tool: Xilinx            |      |

|     | ISE v13.4                                                                       | 100  |

| B.4 | Synthesis results (required slices, maximum clock frequency $f_{\rm max}$ in    |      |

|     | MHz) for the comparison of the reconfigurable LUT multiplier, a generic         |      |

|     | multiplier, and a RCM using ICAP in Section 3.2.4 in Figure 3.3. De-            |      |

|     | vice: Virtex 6 FPGA (xc6vlx75t-2ff484-2). Tool: Xilinx ISE v13.4                | 101  |

| E.1 | Coefficients of the benchmark for the design space exploration in Chap. 6       | .107 |

## **Abbreviations**

ALM adaptive logic module

ALUT adaptive look-up table

ASIC application specific integrated circuit

BLE basic logic element

CCLK configuration clock

CDI configuration data in

CDO configuration data out

CE clock enable

CFGLUT configurable look-up table

CLB configurable logic block

CMM constant matrix multiplication

CSD canonical signed digit

**DA** Distributed Arithmetic

DAG directed acyclic graph

**DSP** digital signal processing

FA full adder

FIFO first-in-first-out buffer

FIR finit impuls response

FPGA field programmable gate array

HDL hardware description language

**HLS** high-level synthesis

IC integrated circuit

#### Abbreviations

ICAP Internal Configuration Access Port

ILP Integer Linear Programming

IP intellectual property

KCM Ken Chapman multiplier

LAB logic array block

LUT look-up table

MCM multiple constant multiplication

MSB most significant bit

OSR optimal shift reassignment

PAG pipelined adder graph

PR Partial Reconfiguration

RAM random access memory

RCA ripple-carry adder

RCM run-time reconfigurable constant multiplier

ReMB reconfigurable multiplier block

RMCM reconfigurable multiple constant multiplier

ROM read-only memory

RPAG reduced pipelined adder graph

SCM single constant multiplication

SD signed digit

SRL shift register look-up table

VHDL very high speed integrated circuit hardware description language

XPE Xilinx Power Estimator

## Author's Publications

The following publications were published during the time of PhD preparation between October 2012 and June 2017. Most of them are included in this thesis.

- M. Kumm, K. Möller and P. Zipf, "Partial LUT Size Analysis in Distributed Arithmetic FIR Filters on FPGAs," in *IEEE International Symposium on Circuits and Systems (ISCAS)*, 2013, pp. 2054–2057.

- [2] M. Kumm, K. Möller and P. Zipf, "Reconfigurable FIR Filter Using Distributed Arithmetic on FPGAs," in *IEEE International Symposium on Circuits and Systems (ISCAS)*, 2013, pp. 2058–2061.

- [3] M. Kumm, D. Fanghänel, K. Möller, P. Zipf and U. Meyer-Baese, "FIR Filter Optimization for Video Processing on FPGAs," in EURASIP Journal on Advances in Signal Processing (Springer), pp.1-18, 2013.

- [4] M. Kumm, K. Möller, and P. Zipf, "Dynamically Reconfigurable FIR Filter Architectures with Fast Reconfiguration," International Workshop on Reconfigurable Communication-centric Systems-on-Chip (ReCoSoC), 2013, pp. 1–8.

- [5] K. Möller, M. Kumm, B. Barschtipan, and P. Zipf, "Dynamically Reconfigurable Constant Multiplication on FPGAs." in Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen (MBMV), 2014, pp. 159–169.

- [6] K. Möller, M. Kumm, M. Kleinlein, and P. Zipf, "Pipelined Reconfigurable Multiplication with Constants on FPGAs," in *IEEE International Conference on Field Programmable Logic and Application (FPL)*, 2014, pp. 1–6.

- [7] K. Möller, M. Kumm, P. Zipf, K. Groß, D.Lens, and H.Klingbeil, "FPGA Based Tunable Digital Filtering for Closed Loop RF Control in Synchrotrons," in GSI Helmholtzzentrum für Schwerionenforschung, Scientific Report, 2014, pp. 331–332.

- [8] K. Möller, M. Kumm, C.-F. Müller, and P. Zipf, "Model-based Hardware Design for FPGAs using Folding Transformations based on Subcircuits," in *International Workshop on FPGAs for Software Programmers (FSP)*, 2015, pp. 7–12.

- [9] K. Möller, M. Kumm, M. Kleinlein, and P. Zipf, "Reconfigurable Constant Multiplication for FPGAs," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 36, no. 6, pp. 927-937, 2017.

- [10] P. Sittel, M. Kumm, K. Möller, M. Hardieck and P. Zipf, "High-Level Synthesis for Model-Based Design with Automatic Folding including Combined Common Subcircuits," in *Methoden und Beschreibungssprachen zur Modellierung und Ver*ifikation von Schaltungen und Systemen (MBMV), 2017.

- [11] P. Sittel, M. Kumm, K. Möller, B. Pasca, M. Jervis and P. Zipf, "Automatic Folding for Model-Based Hardware Design using Isomorphic Subgraphs", currently under review to be published at the *International Conference on Field Programmable Technology (FPT)*, 2017.

- [12] K. Möller, M. Kumm, M. Garrido, and P. Zipf, "Optimal Shift Reassignment in Reconfigurable Multiplication Circuits," accepted for publication in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2017

## 1 Introduction

In this thesis optimization methods to implement run-time reconfigurable constant multipliers (RCMs) on field programmable gate arrays (FPGAs) are proposed. The performance, hardware effort, reconfiguration time and power consumption of resulting circuits are evaluated. The resulting solutions add some important trade-off points to the design space of RCM on FPGAs and make new applications possible.

#### 1.1 Motivation

Multiplication with constants is one of the most frequent operations in digital signal processing (DSP). At the same time, FPGAs have a growing market in DSP applications which were formerly dominated by application specific integrated circuit (ASIC) implementations. Reasons for this trend are the flexibility provided by the re-programmability of FPGAs and increasing ASIC manufacturing costs. The costs of the re-programmability of FPGAs are that FPGA designs are typically larger, slower and consume more power than an equivalent ASIC realization [1]. Therefore, optimized implementations of DSP algorithms for FPGAs are getting more and more important. This is one of the reasons why embedded multipliers are present in the fabric of FPGAs. Nevertheless, the drawback of those fixed coarse-grained blocks is their inflexibility in word size and their limited quantity. Limited quantity is particularly critical in industrial applications when low-cost FPGAs with only few embedded multipliers have to be chosen and other parts of a design are competing for DSP resources. Thus, alternative logic-based methods for constant multiplication are required which are independent of this embedded special purpose hardware but are, on the other hand, efficient enough to narrow the gap to an ASIC realization. Therefore, optimizing the implementation of constant multiplication as shift-add-based circuit is well studied [2-17]. However, switching between a given limited set of constant multiplications during run-time instead of using larger generic multipliers is important, too. Reconfigurable constant multipliers are used to realize hardware efficient run-time adaptable filters [18–21], e.g., for adaptive control and video coding applications. Specifically in [20] an application with tight reconfiguration time and resource constraints is presented, which motivates the necessity of highly optimized RCMs on FPGAs. There, an FPGA is used as co-processor in the control loop of a particle accelerator.

In addition to that, RCMs can be directly integrated into optimized time-multiplexed realizations of linear DSP transforms like DCT and FFT implementations [22,23] and can be used in the context of time-multiplexed resource sharing of linear systems in general. Further applications are multi-stage filters for decimation or interpolation, like polyphase finit impuls response (FIR) filters [24]. Therefore, the implementation of run-time reconfigurable constant multipliers using multiplexers is a well studied research field, too [19, 21, 24–28]. However, most of the previous methods to generate RCMs were optimized to be used on ASICs. On FPGAs long routing delays have to be avoided by inserting registers in the data path. That is why previous RCM solutions perform poor when they are directly applied to FPGAs [29]. As FPGA implementations of DSP applications are getting more and more important, the algorithms presented in this work particularly focus on implementations of RCMs on FPGAs.

Three ways of run-time reconfiguration are distinguished in this work: Logic reconfiguration using reconfiguration using reconfiguration using multiplexers and Partial Reconfiguration (PR). The latter reconfiguration method is provided by the FPGA vendors. However, it comes along with long reconfiguration times and a thereby arising large reconfiguration power consumption. This means, it is not particularly suitable for the above mentioned applications. Therefore, the presented RCM generation methods focus on LUT-based reconfiguration and reconfiguration using multiplexers.

### 1.2 Organization and Contributions of the Thesis

This section gives an overview on the organization of the thesis. Moreover, the main contributions of each chapter are provided.

The background for this thesis is provided in Chapter 2. It gives an introduction to FPGAs as target technology and introduces the different run-time reconfiguration concepts in detail. In addition to that, the background on multiplier-less constant multiplication is provided with a focus on FPGA-specific aspects at the end of the chapter.

Logic reconfiguration using reconfigurable LUTs is covered in Chapter 3. It is shown how reconfigurable constant multiplication based on LUTs can provide hardware optimized RCM solutions, which outperform generic IP core multipliers and non-reconfigurable constant multipliers reconfigured using Partial Reconfiguration. The contributions of this chapter are a new method to generate LUT-based run-time reconfigurable constant multipliers based on Ken Chapman multipliers (KCMs) [30] and two new architectures for LUT-based run-time reconfigurable FIR filters. In addition to a KCM-based FIR filter implementation, an FIR filter architecture based on Distributed Arithmetic (DA) [31,32] and its automatic generation is presented.

An algorithm to generate reconfigurable constant multipliers using multiplexers is presented in Chapter 4. Previous methods on reconfigurable multiplier-less constant multiplication did not consider costs for registers in the combinatorial path of the circuit, which can be used to split up the combinatorial parts during optimization. However, this is important to realize fast FPGA implementations. Moreover, only heuristic solutions for reconfigurable single constant multiplication (SCM) and reconfigurable multiple constant multiplication (MCM) were presented so far. The contribution of this chapter is a new algorithm to generate multiplexer-based run-time reconfigurable constant multipliers for FPGAs including SCM, MCM and their generalization to constant matrix multiplication (CMM). The algorithm considers the insertion of registers during optimization and can be either used to generate optimal solutions or as heuristic, if run-time limitations are present. The C++ implementation of the proposed algorithm is published as open-source [33]. Moreover, the solutions of the proposed algorithm can be used within a high-level synthesis (HLS) flow called Origami HLS [34]. This enables the integration of low-level optimized reconfigurable components in high-level system development.

A post-optimization for multiplexer-based RCMs is described in Chapter 5. It is applicable to all existing RCM solutions for FPGAs and ASICs. The main contribution is a new algorithm based on Integer Linear Programming (ILP) to find an optimal distribution of shifts in given multiplexer-based RCMs.

The different methods of run-time reconfiguration presented in this thesis add some important points to the design space of run-time reconfigurable constant multiplication. The contribution of Chapter 6 is to contrast the different methods in terms of hardware effort, performance, power and reconfiguration time by evaluating this design space using reconfigurable FIR filter implementations.

Finally, Chapter 7 summarizes this thesis and Chapter 8 provides an outlook to future work.

## 2 Background

This chapter provides the background for the following chapters, starting with an overview on field programmable gate arrays (FPGAs), which are the target technology for most of the proposed optimizations. Moreover, the different ways to perform a run-time reconfiguration on FPGAs are presented. This is followed by an introduction to multiplier-less constant multiplication, which also covers FPGA specific aspects of this operation.

## 2.1 Field Programmable Gate Arrays

Field programmable gate arrays (FPGAs) are array-based integrated circuits, which can be programmed and re-programmed on-site. They are regularly structured as two-dimensional array originally consisting of basic logic elements (BLEs) and an interconnecting network. Programmability is achieved by small programmable memories, which change the logic function of BLEs as well as their interconnection. The price for this programmability is that FPGA designs are larger, slower and consume more dynamic power than an equivalent application specific integrated circuit (ASIC) realization [1]. However, FPGAs are widely used with a growing market in the aerospace and consumer electronics and automotive industry. Reasons for the growing market in these industry segments could be a growing demand for high performance digital signal processing (DSP) applications and the flexibility of programming in field, which speeds up system development and allows fast response on changing requirements. Moreover, good performance and a low price are a great advantage to keep the financial risk for small and medium volume developments low. This is not the case for ASICs having large non-recurring engineering costs.

A simplified overview of the basic FPGA layout is given in Figure 2.1. It shows only a small part of an FPGA which typically consists of hundreds of thousands BLEs. Each BLE consists at least of a function generator realized as look-up table (LUT) and a memory element. The input/output ports (IO) as well as the BLEs are connected to the routing network with connection blocks. Some simplified example connections are shown. Moreover, there are programmable routing switches to switch between different routing segments and routing domains. An FPGA can thusly be programmed to implement any logical circuit, only limited by its required hardware resources and interconnection complexity. Since the first FPGAs were commercially introduced in

Figure 2.1: Simplified overview of an FPGA layout.

the mid 1980's by Xilinx, FPGAs are subject to ongoing changes and innovations. Important examples are the inclusion of embedded memories, embedded multipliers and many more specialized hardware units into the FPGA layout to support certain applications.

In the following, details on recent FPGAs of the market leaders Xilinx and Intel are presented. The focus is on the features which are important in the following chapters. More details on technology and features of current FPGAs can be found in text books, e. g., [35] and in the FPGA vendor's handbooks and white-papers, e. g., [36], [37]. The selected device families (Xilinx Virtex 6 and Intel Stratix V) are used in the following chapters for the experimental evaluations. Aspects of other device families are given when important.

#### 2.1.1 Architectural Features

In both device families the BLEs are clustered into larger units called configurable logic block (CLB) in Xilinx FPGAs and logic array block (LAB) in Intel FPGAs. Within these units routing is mainly fixed and only a portion of the number of BLEs inputs is connected to the global routing network. This saves routing resources and reduces the complexity of finding a feasible routing solution.

#### Configurable Logic Block

Each Xilinx CLB consists of two sub-components called slices. As shown in Figure 2.2(a) these slices are connected to the connection block, but are not connected to

Figure 2.2: Xilinx Virtex 6 BLE and its clustering to a slice and a CLB.

each other. Moreover, each slice has a special input and output. These are used to propagate the internal carry in and carry out signals to a slice in the next CLB without using the global routing network. A Virtex 6 slice consists of four BLEs. A simplified overview of one such BLE is shown in Figure 2.2(b). It consists of a 6-input LUT, which can be used as two 5-input LUTs, part of a carry chain to build ripple-carry adders (RCAs) and two optional output registers. Hence, any 6-input-1-output function or any 5-input-2-output function with shared inputs can be mapped to a BLE. For example, a full adder (FA) which is required for an RCA can be implemented using the LUT together with the present XOR gate and carry chain multiplexer. There are several multiplexers for signal routing, which are either used within the application's data flow (drawn with a select input) or configured when the FPGA is programmed (drawn without select input). In addition to that, some special interconnections and multiplexers for advanced features are present, which are not shown here. Important are 3 multiplexers, which can be used to link the four BLE's outputs in a slice. An example of their usage is given in Section 2.2.3. A fully detailed CLB and slice block diagram can be found in the vendor's handbook on Virtex 6 CLBs [36].

#### Logic Array Block

Each Intel LAB consists of ten adaptive logic modules (ALMs) and is connected to the routing network via a connection block (see Figure 2.3(a)). An ALM can be seen as BLE of modern Intel FPGAs. A simplified overview of an ALM is shown in Figure 2.3(b). The shown multiplexers are configured when the FPGA is programmed. The 8-input fracturable LUT can be used to implement a full 6-input LUT or different combinations of LUTs, like, e.g., a 5-input and a 3-input LUT with independent inputs, defined through its configurable output network which is not shown here. All possible configurations can be found in the vendor's device handbook [37]. Like for Xilinx FPGAs two FAs are provided. In contrast to Xilinx FPGAs, the FAs do not require

Figure 2.3: Intel Stratix V ALM and its clustering to an LAB.

any further ALM logic. Similar to Xilinx FPGAs their carry chain is propagated throughout the LAB to the next ALM to enable fast RCA implementations. Four optionally registered outputs are provided to output the adder results as well as the LUT outputs. A detailed LAB and ALM block diagram can be found in the already mentioned handbook. Although the ALMs can be seen as the BLE, the logic utilization on Intel FPGAs is very often given in adaptive look-up tables (ALUTs), which is the estimated number of required half ALMs needed to fit a design.

#### Memory Blocks

Current FPGAs contain numerous small memory blocks which are distributed all over the chip. They can either be used as small independent memory blocks or combined to build larger blocks of random access memory (RAM). There are various possibilities to realize the memory blocks starting from simple single-port memory up to dual-port memory with two read/write ports with various memory array dimensions. The total memory available for the designer ranges from 7 to 39 Mbits within the Virtex 6 device family and 23 to 64 Mbits in the Stratix V device family. Alternatively, the memory blocks can be used as large shift registers, function generators or first-in-first-out buffers (FIFOs).

#### Digital Signal Processing Blocks

As FPGAs are very important in digital signal processing applications, specialized hardware blocks for these applications are part of current FPGAs. As multiplication is the most important operation some more details are given on its implementation. In Virtex 6 FPGAs the DSP block called DSP48E1 slice [38] contains a  $25 \times 18$  bit multiplier. Using DSP blocks including its fixed-size multipliers is thus most favorable when

a multiplier with this size is required. For smaller multipliers or multipliers with other input word sizes other implementations [39] are required. Equally important is the composition to larger multipliers. For this purpose, DSP blocks can be combined using dedicated routing paths between several DSP blocks. Doing this hardware efficient is part of current research [40], [41].

In Intel FPGAs the DSP blocks are implemented more flexible. Realizations of  $9 \times 9$  bit,  $18 \times 18$  bit,  $27 \times 27$  bit and  $36 \times 36$  bit multipliers are provided by the variable-precision DSP blocks in the Stratix V device family [37].

Besides the multiplier, a DSP block includes functional units which are typically required in DSP applications. Without using the general FPGA logic, DSP blocks provide, e. g., adders in front and after the multiplier, bit-wise logic functions and large registers.

#### Routing Delay

Regarding the delay of a circuit, the programmability of FPGAs comes at a price. While in non-programmable integrated circuits local connections have a negligibly small contribution to the overall delay, in FPGAs such a connection can include several routing elements. Moreover, programmable parts within the connection blocks and programmable routing switches add additional delay. A common way to overcome this drawback is to add registers to the initial circuit to split up the combinatorial parts. Introducing registers has to be done systematically to keep the functionality of the original circuit. This is achieved by placing registers in the combinatorial path such that the number of introduced registers on each path from an input to an output is equal. This procedure called pipelining increases the latency of the circuit while keeping its functionality. An overhead of required FPGA resources may occur due to a massiv register insertion. On the other side, it is very likely that unused registers in the FPGA's BLEs, which are already used for logic, will be taken. This was shown, e.g., in [42] by a speedup of 111% of a non-pipelined circuit on a Cyclone II FPGA with a pipelining overhead of only 6%. The more recent FPGAs presented above should provide even better results, as they have double the number of registers per BLE.

#### **Power Consumption**

With an increase in FPGA resources and maximum clock frequency, which can be observed for each new FPGA generation, the power consumption of an FPGA gets more and more important. The power consumed by an FPGA can be separated into the two components static power and dynamic power. Static means, that the power consumption is independent of the switching activity in the device. The main source of static power consumption is transistor leakage current, which tends to increase with decreasing technology size. This is why static power is getting more and more important and consumes a noticeable amount of overall chip power. Dynamic power consumption

$P_{ ext{dyn}}$  is related to the actual switching activity. It can be basically summarized as product of the capacitance C of the considered component and the supply voltage V squared, multiplied by the frequency f and the switching activity  $\alpha$ .

$$P_{\rm dyn} = CV^2 f\alpha. (2.1)$$

Supply voltage and capacitance are technology dependent, hence, the only way to reduce the dynamic power consumption for a given technology is by reducing the frequency or the switching activity within the circuit. One way to reduce the switching activity is again pipelining. It helps to reduce glitches and thereby dynamic power consumption [43]. In the context of run-time reconfiguration switching activity caused by changing logical functions during reconfiguration should be reduced. In signal processing applications the energy required to compute one data sample is an important figure. It can be calculated by relating the dynamic power  $P_{\rm dyn}$  to the sample rate given in  $\left[\frac{\rm samples}{\rm ns}\right]$  as

$$E_{\rm s} = \frac{P_{\rm dyn}}{\rm sample\ rate} \tag{2.2}$$

Moreover, the reconfiguration energy  $E_{\rm rec}$  is important to compare different reconfiguration approaches. It is computed as

$$E_{\rm rec} = P_{\rm rec} T_{\rm rec} \,, \tag{2.3}$$

while  $P_{\text{rec}}$  is the average power consumption during reconfiguration and  $T_{\text{rec}}$  is the reconfiguration time.

### 2.1.2 Design Flow

In the last sections some important aspects of hardware resources, their routing, timing and power consumption on FPGAs were presented. Mapping a system to an FPGA offers many trade-offs with respect to these aspects and requires several steps. These steps are shown in the diagram in Figure 2.4 and explained in the following.

The initial step is the design and simulation of the system for a specific application with specific requirements. This can be an algorithmic description, C/C++ code or a model-based design description in, e.g., Matlab/Simulink or LabVIEW. At this point a decision has to be made which parts of the design should be implemented on an FPGA (hardware). This can be the whole system or only parts of the system if the FPGA is used as co-processor in a hardware-software co-design. After this step, the hardware parts have to be transformed into a representation which can be processed by their synthesis tools (e.g., Xilinx ISE, Vivado, Intel Quartus Prime).

The entry point for the FPGA design flow with these tools can be a hardware description written in a hardware description language (HDL) like very high speed inte-

Figure 2.4: Diagram of the steps required to map a system specification to an FPGA.

grated circuit hardware description language (VHDL) or Verilog HDL or a hardware description provided as schematic. All descriptions can include custom blocks called intellectual property (IP) cores, provided by the FPGA vendors or a third party. IP cores are special implementations of a certain function ranging from low complexity operations up to processors. A simulation can be used to verify the functional behavior of the hardware description by comparing it to the initial system design or pre-calculated test data.

The first step performed in the FPGA design flow is the translation of the hardware description into a netlist, called *Synthesis*. A netlist is basically a textual description of the circuit including all components, required IO ports and their interconnection. This step can include target specific optimizations like, for example, removing unused signals or detecting certain functional units. In the next step, the components in the netlist are matched with the physical resources of the target FPGA. This process called *Mapping* is accompanied by some optimizations and design rule checks.

Once the components are mapped to the existing FPGA components, they have to be assigned to specific resources of the FPGA. Moreover, their interconnection has to be realized by the available routing resources. Assignment and interconnection are done during *Place and Route*. In addition to that, a timing analysis is included or implemented as an additional step after *Place and Route*. During the timing analysis the timing information of the final routed netlist, including delays of components, wires, interconnections and routing switches, is collected.

This timing information can be used for a realistic simulation of the circuit represented by the netlist. Moreover, a *Power Analysis* based on timing-accurate switching activity can be performed. For that purpose the netlist including the timing information can be exported and simulated using a test bench. VHDL simulation tools like,

e.g., ModelSim [44] are able to output the full simulation data into a file. This file together with the netlist are used as input to the *Power Analysis*.

If all requirements and design constraints are fulfilled, the last step is the *Programming* of the FPGA. For this purpose, the netlist after *Place and Route* is stored as a bit file. Each bit in this file indicates if a specific bit in the FPGA configuration (routing and logic) is set. *Programming* thus means in this context, setting all required configuration bits by sequentially streaming the bit file content into the FPGA.

## 2.2 Run-Time Reconfiguration on Field Programmable Gate Arrays

Besides the full reconfiguration, referred to as *Programming* in the last section, reconfiguration of parts of the FPGA during run-time has become an important feature of recent FPGAs. There are basically three ways to perform such a run-time reconfiguration on FPGAs:

- 1. Partial reconfiguration including routing and logic with partial bit files.

- 2. Logic reconfiguration using run-time reconfigurable LUTs.

- 3. Routing reconfiguration using multiplexer-based resource sharing.

The investigation of their influence on the required hardware resources, resulting performance, power consumption and reconfiguration time in the context of reconfigurable constant multiplication is a main part of later chapters (logic reconfiguration in Chapter 3, routing reconfiguration in Chapter 4 and Chapter 5). The following three sections provide the required background information and implementation details for the aforementioned methods.

#### 2.2.1 Partial Reconfiguration

A great advantage of FPGAs is that they can be programmed on-site and that they can be re-programmed, instead of a re-fabrication as required for non-programmable integrated circuits. This design flexibility is even higher with Partial Reconfiguration (PR) [45], [46]. PR is available for the latest FPGAs, namely the Intel Arria V, Cyclone V, Stratix V, Arria 10 device families and Xilinx Virtex 4-6, 7 series and UltraScale device families. Mutually exclusive designs can be placed in the same region of the FPGA. For this part of the FPGA, logic functions and routing can be exchanged dynamically, while the remaining parts of the device continue to operate unaffected. To do so, bit files for these reconfigurable regions are created in the design phase by dividing the FPGA into reconfigurable and static logic.

The smallest size of a reconfigurable region in the Xilinx tool flow corresponds to a certain number of CLBs, called configuration frame. A good overview over the

| FPGA family | CLBs per frame    | DSP48 per frame   | Block RAM per frame |

|-------------|-------------------|-------------------|---------------------|

| Virtex 4    | 16 high by 1 wide | -                 | -                   |

| Virtex 5    | 20 high by 1 wide | -                 | -                   |

| Virtex 6    | 40 high by 1 wide | -                 | -                   |

| 7 series    | 0 0               | 10 high by 1 wide | 10 high by 1 wide   |

| UltraScale  |                   | 24 high by 1 wide | 12 high by 1 wide   |

Table 2.1: Frame size for the different Xilinx FPGA families.

composition of a Xilinx bit stream can be found in [47]. The size of a configuration frame for the different Xillinx FPGA families can be found in Table 2.1. The smallest PR design for a Xilinx Virtex 6 FPGA will, for example, block at least (if routable) 40 CLBs, which equals 80 slices. This is important as a reconfiguration port is used to exchange the partial bit files. This causes a certain reconfiguration time. For the Xilinx FPGAs the partial bit file can be loaded, e.g., via the Internal Configuration Access Port (ICAP), which is a 32 bit wide interface running at 100 MHz. This results in a theoretical maximum reconfiguration speed of 400 MB/s. Experimental results by Liu et al. [48] show that a maximum reconfiguration speed of 371.4 MB/s is possible. With a size of 93312 bit per frame, the minimal ICAP reconfiguration time for Xilinx Virtex 6 FPGAs is about 29 µs. Further details on Xilinx PR can be found in the vendor handbooks, e.g., [45].

In the Intel PR flow each LAB, RAM block, DSP block and routing multiplexer can theoretically be reconfigured individually. However, like for Xilinx FPGA the reconfiguration time depends on the size and orientation of the reconfigurable parts of the design. The partial bit file can be loaded, e.g., via the PR Region Controller IP block which provides an up to 32 bit wide configuration data interface. With an interface speed of up to 250 MHz reported in the vendor handbooks [46] considerably small reconfiguration time overheads should be possible with Intel FPGAs if only a small portion of the design has to be reconfigurable.

# 2.2.2 Logic Reconfiguration using Dynamically Reconfigurable LUTs

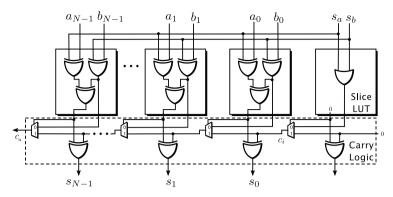

In modern Xilinx FPGAs, namely Virtex 5/6, Spartan 6 and the whole 7 series [49] a special dynamically reconfigurable LUT, called configurable look-up table (CFGLUT), is provided. It is available by using the HDL primitive *CFGLUT5* in the Xilinx tools ISE and Vivado, respectively. Reconfigurable means that the LUT contents realizing a certain logic function can be changed during run-time. Fig. 2.5(a) shows the interface of such a CFGLUT, which has five LUT inputs and can be used as a 5-input-1-output logic

Figure 2.5: Specialized Xilinx FPGA components to enable LUT reconfiguration: (a) interface of a Xilinx CFGLUT, (b) reduced block diagram to show the functionality of a Xilinx shift register LUT.

function or as 4-input-2-output logic function when input I4 is tied to a logical one. One CFGLUT utilizes the slice resource of a standard 6-input LUT. It provides a special reconfiguration interface with the signals configuration data in (CDI), configuration data out (CDO), clock enable (CE) and configuration clock (CCLK). A new output function can be loaded by shifting a new 32 bit LUT configuration sequentially into CDI, while CE is tied to a logical one, following the clock CCLK. At the same time, the previous LUT configuration is shifted out of CDO. This property can be used for a serial reconfiguration of several CFGLUTs. Reconfiguration of CFGLUTs in parallel takes 32 CCLK clock cycles, while the time for a serial reconfiguration has to be multiplied by the number of serially connected CFGLUTs. This means, reconfiguration time is in the range of some hundred ns, dependent on CCLK (typically between 200 and 500 MHz) and the selected reconfiguration mode (parallel or serial).

In fact, the implementation of the so called shift register look-up table (SRL) with clock enable, which was already present in older FPGAs, e.g., Virtex II and Spartan 3, is reused. A simplified block diagram of the SRL circuit with only two LUT inputs is shown in Fig. 2.5(b).  $D_{\rm in}$  is the input of a delay chain, which is enabled by CE. A multiplexer is used to select a delayed value of  $D_{\rm in}$  using the inputs I0 and I1. Replacing  $D_{\rm in}$  by CDI and  $Q_3$  by CDO in Fig. 2.5(b) would lead to a CFGLUT with 4 configuration bits. Thus, SRLs provide the same logic reconfiguration possibility as CFGLUTs. Therefore, a certain backwards compatibility for older Xilinx FPGAs is given for architectures based on CFGLUTs.

For Intel FPGAs the reconfigurable LUT is not available. Shift registers are present, but realized as a chain of ALM output registers. Thus, they can not be used like a CFGLUT and would require a multiple of hardware resources. Block RAM which is present on most of the modern FPGA families could be used instead [50]. This comes with drawbacks in the resulting routing and a lower performance. Moreover, the

availability of a sufficient quantity of available RAM could be critical, if other parts of the design are competing for this resource.

# 2.2.3 Routing Reconfiguration using Logic Multiplexers on FPGAs

The programmable routing of an FPGA is fixed during run-time. However, multiplexers realized with BLEs can be used to change signal routing during run-time. This is especially interesting in the context of switching between the different circuit alternatives for resource sharing like, e.g., in multiplexer-based run-time reconfigurable constant multipliers (RCMs), which are the topic in Chapter 4. Besides their mapping into the soft logic (slices/ALMs) as shown in the following, the mapping of multiplexers onto otherwise unused DSP blocks has been investigated [51], too.

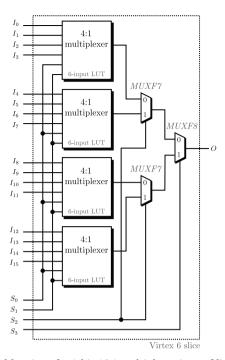

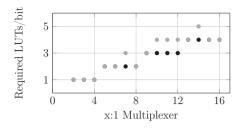

A Virtex 6 slice [36] consists of four 6-input LUTs, which can be used as any 6-input logic function (see Section 2.1.1). Hence, each LUT can be used as an up to 4:1 1-bit multiplexer. Moreover, the Virtex 6 slice includes two 2:1 multiplexers (MUXF7) to switch between two of the LUT results, which extends the usage to two up to 8:1 1-bit multiplexers. Finally, there is another 2:1 multiplexer (MUXF8) to switch between the outputs of the two MUXF7s. This means, four LUTs (= one slice) are required to build an up to 16:1 1-bit multiplexer as shown in Figure 2.6. Two of those 16:1 multiplexers can be combined to a 32:1 1-bit multiplexer utilizing only one additional LUT and so on. Using Primitives [36] in the VHDL description makes it possible to use the slices exactly in that way. This results in an optimized multiplexer implementation first proposed by Chapman [52]. The gain of this implementation can be seen in Figure 2.7 with results originally published in [29]. It shows the LUT consumption of the mapping achieved by Xilinx ISE 13.4 (gray) and the improved solution by using *Primitives* (black when better, otherwise equal to ISE mapping) for 2:1 to 16:1 multiplexers. The operating frequency is not shown, due to the fact that only one slices is required, which leads to frequency estimations that are unrealistic for a final design, as there should be more limiting parts elsewhere.

As shown before, an Intel ALUT in a Stratix V ALM can be used to map a variety of different LUT configurations up to a 7-input function in some cases. In the case under consideration each ALUT (half ALM) can implement an up to 4:1 1-bit multiplexer. The 8-input fracturable LUT does not provide a specialized multiplexers implementation within one ALM. Synthesis results showed that large multiplexers are built as a cascade of 4:1 multiplexers. Each cascaded multiplexer except the first one, can process three additional multiplexers. This results in an estimated ALUT consumption of

$$\#ALUTs = \left\lceil \frac{\#\text{multiplexer inputs} - 1}{3} \right\rceil$$

(2.4)

Figure 2.6: Mapping of a 1 bit 16:1 multiplexer into a Virtex 6 slice.

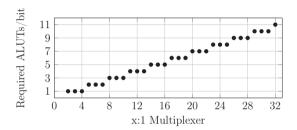

To ensure this assumption is correct, multiplexers with different input word sizes ranging from a 2:1 to a 32:1 were mapped on a Stratix V FPGA using Quartus Prime 15.1. The resulting average values for required ALUTs per bit for up to 32 multiplexer inputs can be found in Figure 2.8. These numbers confirm equation 2.4.

# 2.2.4 Evaluation of Run-Time Reconfigurable Designs

Important properties for the evaluation of a design implemented on an FPGA are classically its resource usage, performance, and power consumption. The resource usage and power consumption reflect costs of the considered design and can therefore be used to compare different implementations of the same functionality. The required FPGA gets more expensive as the required resources increase. An increased power consumption will limit the battery life time in a mobile application or will in general raise the operating costs. Moreover, the design of the overall system can get more complicated, when the FPGA's peak power consumption becomes critical. The performance, often given as maximum possible operating speed, is a number to decide whether the given implementation is suitable for a certain application or not. However, the required resources are not always independent from a given performance constraint. Pipelining can be used, as described before, to reduce the routing delay, which on the other hand

Figure 2.7: Required LUTs per bit for an x:1 multiplexer on a Virtex 6 FPGA. ISE solution (gray) and improvement by *Primitive* usage, using the multiplexer implementation described by Chapman.

Figure 2.8: Required ALUTs per bit for an x:1 multiplexer on a Stratix V FPGA using Ouartus.

can increase the required resources. Therefore, if no specific performance constraint is given, the compared implementations should have a similar performance or, at least, the trade-off between required resources and performance should be shown.

In the context of run-time reconfiguration the reconfiguration time, required configuration memory and reconfiguration power of a design have to be evaluated. Again, a separation into costs and application dependency is possible. The configuration memory and reconfiguration power can increase the overall system's costs by a larger hardware requirement and design complexity, respectively. The required reconfiguration time is application dependent and may exclude some run-time reconfigurable design variant from a certain application.

#### Resources and Performance

To get realistic numbers for the above-mentioned design properties an FPGA synthesis has to be performed. The resulting resource consumption as well as the maximum possible operating speed can be directly gained from the netlist after place and route. While the provided numbers for the required resources represent the real resource consumption for the given netlist, these numbers are strongly dependent on synthesis options and algorithms. They can hence differ for a slight change in the design description or in the synthesis random seed over different FPGA synthesis runs leading to different

netlists. Nevertheless, comparing resources after place and route is the de facto standard when different implementations targeting FPGAs are compared. Moreover, during experimental evaluations it could be observed, that the reported resource consumption is meaningful and in the same range for equally complex designs with slightly different design descriptions [29,53]. The given numbers after place and route will, therefore, be used to compare different design implementations. In non-pipelined designs the number of required LUTs is often a good representation of required resources. However, for designs containing many registers—like pipelined designs—the utilization of BLEs plays a major role. Therefore, the number of required BLEs (slices/ALMs) should be considered. The maximum possible operating speed provided by the vendor tools is a lower bound estimate. This is sufficient to determine if the analyzed design meets given requirements.

#### **Power Consumption**

The power consumption for FPGAs can be estimated using the vendor tools or measured using high precision amplifiers and an oscilloscope [47], [54]. Estimation is done by summing up the power of used resources based on their switching activity (cf. Section 2.1.1). Moreover, the resulting data depends on an FPGA specific capacitance model provided by the FPGA vendors. It was shown by Becker et al. [55] by a comparison to a power measurement that the data gained by the vendor tool Xilinx Power Estimator (XPE) [56] is reliable. Therefore, XPE is used for the analysis of run-time reconfigurable circuits in Chapter 6. For this purpose a netlist after *Place and Route* is simulated using ModelSim [44] using random input data. Then, the simulated switching behavior as well as the netlist are used as input for the power analysis in XPE.

However, XPE does not provide a method to estimate the power consumption of the partial reconfiguration process described in Section 2.2.1. While there are investigations how to model reconfiguration power, e.g. by Bonamy et al. [47], a power estimation tool for PR power is still not available.

#### Reconfiguration Time and Reconfiguration Memory

The reconfiguration time and reconfiguration memory depend on the used reconfiguration approach. For the multiplexer-based approaches the configuration can be changed from one clock cycle to the other and no reconfiguration memory is required. For the LUT-based approach (cf. Section 2.2.2) the reconfiguration time depends on the reconfiguration mode (serial or parallel) and the required configuration memory. The configuration memory can be calculated in advance based on the number and size of reloadable output functions. Further details on the determination of reconfiguration time and configuration memory are provided in Chapter 3. In the context of PR the configuration time depends on the reconfiguration memory and the used configuration interface. The size of the configuration memory is identical to the size of the partial

bit file. However, this bit file is strongly dependent on the number of required configuration frames (cf. Section 2.2.1). This number can not be calculated or estimated in advance and requires an FPGA synthesis. Nevertheless, following the arguments given for the resource consumption, the numbers after place and route can be used for a comparison of reconfiguration time and reconfiguration memory to other approaches.

# 2.3 Constant Multiplication on Integrated Circuits

After this FPGA-specific introduction to run-time reconfiguration, this section provides the background on multiplier-less constant multiplication. Multiplication with constants is an essential arithmetic operation and used in nearly any DSP algorithm. The implementation of this operation on integrated circuits (ICs) is thus a well studied research topic. Instead of using generic multipliers, constant multiplication is implemented multiplier-less using additions, subtractions and bit shifts. This is advantageous as bit shifts can be realized as wires on ICs and special properties in the constant's number representation can be individually exploited.

## 2.3.1 Single Constant Multiplication

Consider two unsigned binary numbers  $x = \{x_{B_{x-1}}x_{B_{x-2}}\dots x_0\}$  and  $c = \{c_{B_{c-1}}c_{B_{c-2}}\dots c_0\}$ . The multiplication of these two numbers is

$$xc = x \sum_{b=0}^{B_c-1} 2^b c_b = \sum_{b=0}^{B_c-1} 2^b x c_b.$$

(2.5)

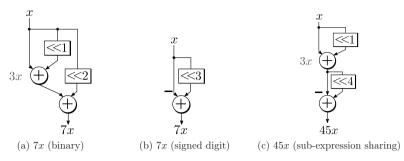

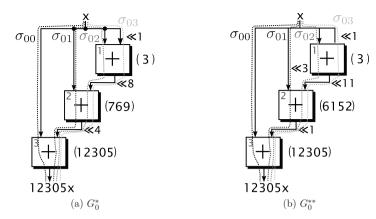

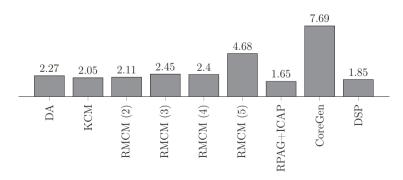

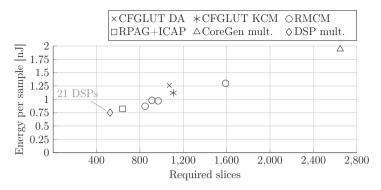

As a  $c_b$  of zero has no contribution to the result, multiplication by a constant can be reduced to the sum of all products  $xc_b$  for which  $c_b$  is one, weighted by  $2^b$ . Note that a multiplication by  $2^b$  corresponds to a left shift by b bit of a binary number. The number of shifted inputs to be added is the number of digits in c which are not zero. This number of so called non-zeros can be reduced when a different number representation is used. The representation of a number in the signed digit (SD) representation [2] includes the values 1,0 and -1 for a digit (-1 will be noted as  $\overline{1}$  in the following). While the unsigned representation of the decimal number 7 is  $111_{\text{bin}}$  (three non-zeros), an SD representation of  $7_{\text{dec}}$  is  $100\overline{1}_{\text{SD}}$  (two non-zeros). This means, the multiplier-less multiplication by 7 needs two instead of three additions/subtractions when an SD representation is used. The resulting multiplication circuits are shown in Figure 2.9(a) and 2.9(b). A subtraction is shown as addition with a negative input. In the following addition and subtraction will be summarized in the term addition, as the resulting hardware effort is nearly the same for both operations.